Les mémoires vives dynamiques, DRAM.

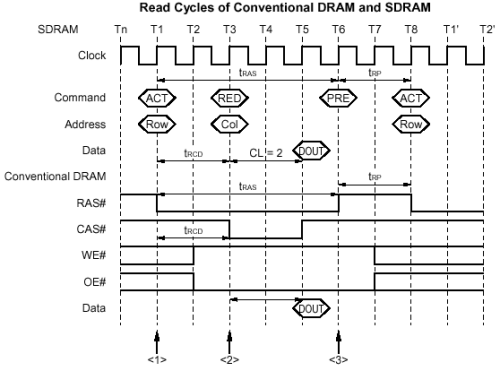

Du fait de leur très

grande densité d'intégration, les

mémoires vives dynamiques DRAM

doivent recourir à un multiplexage des adresses pour

connaître la position de la cellule adressée. Les bits de l'adresse

d'entrée sont donc associés à deux signaux supplémentaires

qui indiquent à la mémoire si l'adresse est celle des lignes

(RAS) ou celle des colonnes (CAS). Le chargement

de la position d'une cellule de mémoire se fait donc en deux temps

:

- chargement de l'adresse de la ligne de la cellule recherchée (Adresse

et signal RAS actifs),

- chargement de l'adresse de la colonne de cette cellule (Adresse et signal

CAS actifs).

De plus, ces mémoires

intègrent un compteur de rafraîchissement

qui gère l'adressage des lignes à rafraîchir. Le mode

de rafraîchissement peut se faire:

- soit entre des modes de lecture et d'écriture standard, on parle

alors de rafraîchissement distribué,

- soit en bloquant les accès en lecture et en écriture pour

rafraichir la totalité des cellules, on parle alors de rafraîchissement

en rafale. Dans ce dernier cas, ce rafraîchissement occupe

plus de temps en une seule fois mais est opéré moins fréquemment.

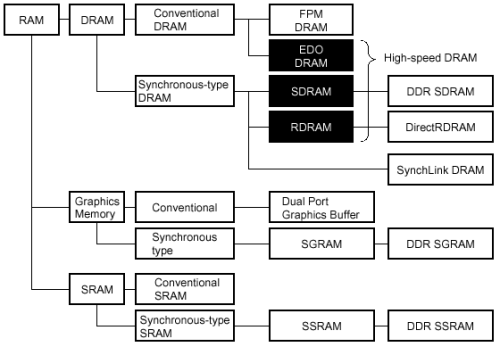

Les différents types de mémoires DRAM

Il existe de nombreux types

de mémoires vives, mais on distingue essentiellement les :

1 - FPM DRAM (Fast Page Mode

DRAM)

2 - EDO DRAM (Extended Data

Out DRAM)

3 - SDRAM (Synchronous DRAM)

4 - RDRAM (Rambus DRAM)

5 - DDR SDRAM (Double Data Rate

SDRAM)

6 - SynchLink DRAM

7 - Dual Port Graphics Buffer

8 - SGRAM (Synchronous Graphics

RAM)

9 - DDR SGRAM (Double Data Rate

SGRAM)

10 - SSRAM (Synchronous SRAM)

11 - DDR SSRAM (Double Data

Rate SSRAM).

Pour plus de renseignements concernant toutes ces mémoires vives, il faut se reporter aux documents des fabricants.

On trouvera d'excellents renseignements dans le manuel d'utilisation des mémoires synchrones de la société Elpida, filiale de NEC.