3 - Les GALs.

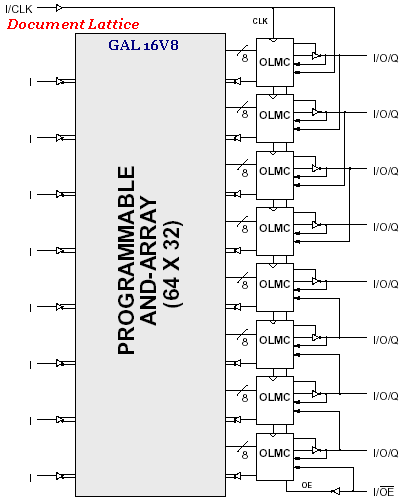

Pour remédier à ces deux problèmes, les GALs furent

réalisés en technologie CMOS diminuant ainsi la consommation

énergétique. Disposant de macrocellules en sortie, ils peuvent

être configurés comme des circuits purement combinatoires

ou comme des circuits de type registre. L'une des possibilités

est d'émuler complètement le fonctionnement des PALs grâce

à la programmation des macrocellules de sortie (OLMC = Output Logic

Macro Cell). Le GAL 16V8 du schéma ci-contre permet par exemple

une totale émulation du PAL de même référence.

Une cellule OLMC peut être

programmée selon un mode de fonctionnement, simple, complexe ou

mémoire (register). Cette programmation est totalement transparente

pour l'utilisateur grâce au logiciel associé. En mode simple

les sorties peuvent être, ou bien des sorties combinatoires, ou

bien des entrées supplémentaires (émulation des PAL10L8

et 12P6). En mode complexe, ces sorties peuvent être programmées

comme des sorties ou des entrées/sorties (équivalence avec

les PAL16L8 et 16P8). En mode registre, les macrocellules peuvent être

configurées comme des entrées/sorties ou comme des bascules

de mémorisation (émulation des PAL16R8 et 16RP4)

Leur principal inconvénient est le bruit parasite provoqué pendant

les commutations.

Ces circuits GALs sont effaçables électriquement

(technologie E2CMOS) et peuvent ainsi être reprogrammés plusieurs

fois.

4

- Les CPLDs et les FPGAs.

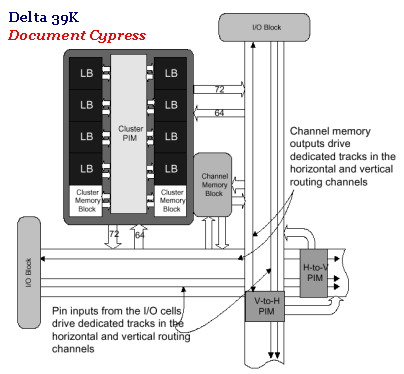

Les CPLDs (Complex Programmable Logic Devices), réalisés

en technologie CMOS, sont tout à la fois rapides et très

denses, de 30 000 à 200 000 portes logiques, tout en étant

peu gourmands en énergie. Ils sont organisés en groupes

de blocs logiques connectables entre eux par des pistes horizontales et

verticales. Chaque groupe contient plusieurs blocs logiques et des blocs

de mémoire. Chaque groupe logique est adjacent à un groupe

de mémoire lui même directement accessible par les broches

d'entrée/sortie (voir

document ci-contre).

Les FPGAs (Field Programmable Gate Array) sont des matrices de portes programmables de très grande densité d'intégration (environ 100 fois plus qu'un PAL). Les FPGA ont une architecture basée sur des modules logiques (constitués en blocs), des pistes de routage et des connections par antifusibles (voir document ci-contre).