Chaque trame, chaque paquet, contient un champ de test d'erreurs. Si dans les transmissions simples on pouvait se contenter de quelques bits supplémentaires (bits de parités) afin de réaliser un système autocorrecteur, comme le code de Haming, la plupart des systèmes utilisent aujourd'hui un code de redondance cyclique (CRC).

Des sommes de contrôle (cheksum) sont également utilisées, comme par exemple pour la vérification des adresses Ethernet.

Une adresse Ethernet est connue sur 6 octets, Ad5 Ad4 Ad3 Ad2 Ad1 Ad0. Dans ce cas la somme de contrôle Ck est une valeur de 16 bits obtenue de la façon suivante :

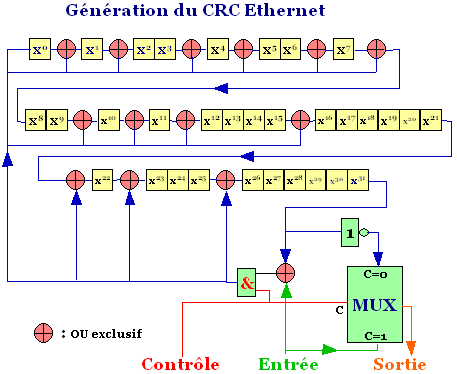

Chaque trame contient un champ de détection des erreurs, de 32 bits pour une trame Ethernet, obtenu par un calcul mathématique utilisant un polynôme de redondance cyclique.

Le

principe revient à calculer le reste de la division du nombre binaire,

correspondant aux données envoyées, par un nombre binaire appelé

polynôme générateur ou CRC, connu de l'émetteur

et du destinataire.

Ce reste est accolé aux données et envoyé à leur

suite par l'émetteur. Le destinataire le recalcule à partir

des données reçues et vérifie qu'il est bien égal

au reste reçu à la suite des données. Sinon il peut redemander

la réémission de cette trame.

Le CRC le plus utilisé est le CRC du CCITT

L'adresse

Ethernet est donc complétée par deux octets Cd1 et Cd0 tels

que Ck=Cd1.256 + Cd0 .

Par exemple, l'adresse F0

2E 15 6C 77 9B devient avec son cheksum F0

2E 15 6C 77 9B 63

2F

Cette somme de contrôle peut être calculée en utilisant un glissement à gauche du complément arithmétique binaire, avant de faire la somme des trois paires d'octets, comme le montre le programme ci-dessous.

Var Ad0,Ad1,Ad2,Ad3,Ad4,Ad5;

Var Octet : Array[0..5] of integer;

Octet[0]:=Ad5; Octet[1]:=Ad4; Octet[2]:=Ad3;

Octet[3]:=Ad2; Octet[4]:=Ad1; Octet[5]:=Ad0;

Ck:=0;

for i:=0 to 2

begin

L'avantage

de procéder à une division est que celle-ci peut s'effectuer

au fur et à mesure des bits émis (ou reçus), avant

même de connaître la totalité des données à

émettre.

On utilise pour cela un registre

à décalage bouclé, initialement préchargé

avec des 1, ainsi qu'une structure de base de multiplexage de

deux voies vers 1 utilisant une structure à deux transistors

complémentaires MOS (CMOS délà utilisés

avec les

arbres de décision binaire). (Voir

le fonctionnement)

Tant qu'il y a des bits de données à émettre, le bit

de Contrôle est à

1, ce qui a pour effet de charger les bits de données présents

en Entrée dans le registre

à décalage, tout en transmettant chaque bit vers la Sortie.

Lorsque

tous les bits de données ont été transmis, alors le bits

de Contrôle passe à

0, faisant ainsi basculer le multiplexeur de sortie vers le CRC

obtenu, dont tous les bits, complémentés, sont alors envoyés

en ligne.

Le récepteur procède de la même façon. Mais

lorsqu'il a reçu tous les bits de données, il continue à

charger le registre à décalage, en maintenant le bit de

Contrôle à

1. Il charge donc le CRC créé par l'émetteur.

Lorsqu'il a terminé, les bits présents dans le registre

à décalage doivent, s'il n'y a pas eu d'erreur de transmission,

prendre la valeur suivante :

110001110000010011011101111011

= C704DD7B

en

commençant par le bit de plus fort poids (MSB=Most Significant

Bit), et en terminant par celui de plus faible poids binaire (LSB = Least

Significant Bit). Voir

le fonctionnement du générateur de CRC.

if Ck>=65536 then Ck:=Ck - 65535;

Ck:=Ck + Octet[2*i]*256 + Octet[2*i + 1];

if Ck>=65536 then Ck:=Ck - 65535;

if Ck=65535 then Ck:=0;

Cd1:=Ck div 256;

Cd0:=Ck mod 256;