Protection des entrées contre une décharge électrostatique.

Afin de protéger les entrées contre une décharge électrostatique (la tension de claquage de la silice isolante entre la grille et le canal est faible ~100 V), une première solution a été de placer des diodes d'écrêtage entre chaque entrée et les tensions d'alimentation Vss et Vdd.

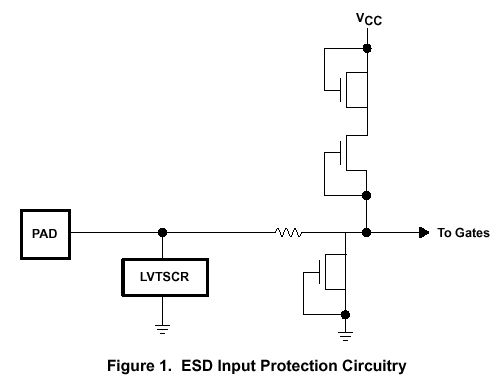

Une résistance est également ajoutée en entrée et un dispositif de redressement contrôlé au silicium (SCR analogue à un thyristor), déclenchant sous une faible tension (Low Voltage), est également placé en entrée dans certains circuits (famille HCT de Texas Instrument par exemple).

On remarquera sur la figure ci-contre que les deux diodes d'écrêtage ont été remplacées par des transistors d'arrêt (clamp transistors) qui doivent donc fonctionner en avalanche lors d'une décharge électrostatique et protéger ainsi l'oxide de silicium placé entre la grille et le canal.

La protection des sorties utilise le même principe.