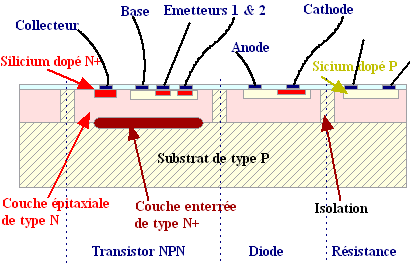

La technologie TTL

L'intégration des circuits

TTL dans le silicium se fait avec la technique planar dont les avantages sont

mutiples :

- les multi-émetteurs en entrée occupent moins de place que

les diodes,

- les circuits TTL sont environ deux fois plus rapides que leurs équivalents

DTL,

- la sortie TTL, dite "totem-pole",

présente une faible impédance de sortie, aussi bien au niveau

haut qu'au niveau bas, augmentant ainsi sa vitesse lors de charge capacitive

(diminution de la constante de temps t=RC).

Afin de permettre un câblage

en ET en sortie, des circuits collecteur

ouvert ont également été produits.

Pour réaliser l'interconnection de plusieurs sorties sur des bus

d'informations, des

sorties trois états ont également été

mises au point.

A la technologie TTL standard, produite dès 1964, ont été ajoutées les familles TTL Low Power (L), High Speed (H), Schottky (S) et Low Power Schottky (LS).

Par exemple, pour améliorer le facteur vitesse, les résistances ont été diminuées. Ceci s'est fait au détriment de la puissance dissipée, le produit vitesse puissance restant à peu près constant.

L'introduction d'une diode rapide à faible tension de seuil, du type Schottky, entre la base et le collecteur des transistors, permet d'éviter la sursaturation de ceux-ci et d'augmenter ainsi la vitesse du circuit sans pertes Joule supplémentaires.

De nombreuses autres familles ont ensuite vu le jour, AS (Advanced Schottky), ALS (Advanced Low Power Schottky), Fast (F), ...